Haut op der allgemeng benotzt héich-MuechtMOSFEThiren Aarbechtsprinzip kuerz virzestellen. Gesinn wéi et seng eege Aarbecht realiséiert.

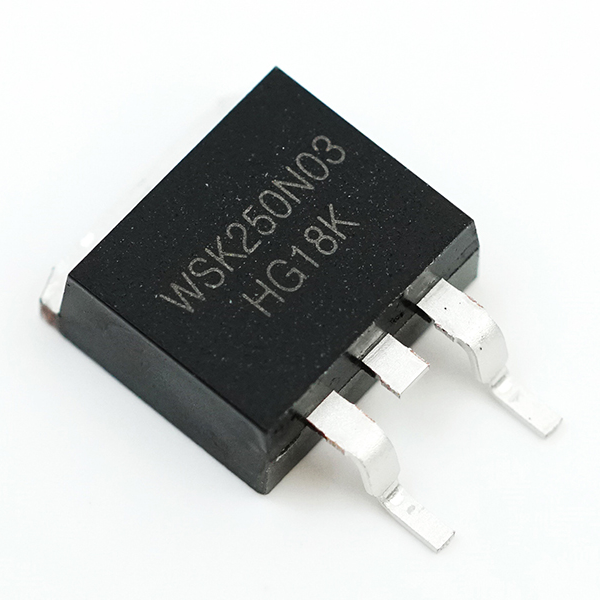

Metal-Oxide-Semiconductor dat ass, Metal-Oxide-Semiconductor, genee, dësen Numm beschreift d'Struktur vum MOSFET am integréierte Circuit, dat ass: an enger bestëmmter Struktur vum Halbleiterapparat, gekoppelt mat Siliziumdioxid a Metall, d'Bildung vum Paart.

D'Quell an d'Drain vun engem MOSFET sinn opposéierbar, béid sinn N-Typ Zonen, déi an engem P-Typ Backgate geformt sinn. An deene meeschte Fäll sinn déi zwee Beräicher d'selwecht, och wann déi zwee Enden vun der Upassung net d'Performance vum Apparat beaflossen, sou en Apparat gëtt als symmetresch ugesinn.

Klassifikatioun: no der Kanal Material Typ an isoléiert Gate Typ vun all N-Kanal an P-Kanal zwee; laut dem konduktiven Modus: MOSFET ass an Ausschöpfung an Erhéijung opgedeelt, sou datt MOSFET an N-Kanal Ausschöpfung a Verbesserung opgedeelt ass; P-Kanal Verarmung a Verbesserung vu véier Haaptkategorien.

MOSFET Prinzip vun Operatioun - déi strukturell Charakteristiken vunMOSFETet féiert nëmmen eng Polaritéit Träger (Polyen) déi am konduktiv involvéiert sinn, ass en unipolare Transistor. Leedungsmechanismus ass d'selwecht wéi de Low-Power MOSFET, awer d'Struktur huet e groussen Ënnerscheed, Low-Power MOSFET ass en horizontalen konduktiven Apparat, de gréissten Deel vun der Power MOSFET vertikale conductive Struktur, och bekannt als de VMOSFET, wat de MOSFET staark verbessert Apparat Spannung a Stroum widderstoen Fäegkeet. D'Haaptrei Fonktioun ass, datt et eng Layer vun Silica Isolatioun tëscht der Metal Paart an de Kanal ass, an huet dofir eng héich Input Resistenz, der Rouer féiert an zwee héich Konzentratioune vun n Diffusioun Zone engem n-Typ konduktiv Kanal ze Form. n-Kanal Verbesserung MOSFETs mussen op de Paart mat Forward Bias applizéiert ginn, an nëmmen wann d'Gate Quell Volt méi grouss ass wéi d'Schwellspannung vun der konduktiv Kanal generéiert vun der n-Kanal MOSFET. n-Kanal Ausarmungstyp MOSFETs sinn n-Kanal MOSFETs, an deenen d'Leedungskanäl generéiert ginn wann keng Gatespannung ugewannt gëtt (Gatequellspannung ass null).

De Prinzip vun der Operatioun vum MOSFET ass d'Quantitéit vun der "induzéierter Ladung" ze kontrolléieren andeems Dir VGS benotzt fir den Zoustand vum konduktive Kanal ze änneren, deen duerch d'"induzéiert Ladung" geformt gëtt, an dann den Zweck z'erreechen fir den Drainstroum ze kontrolléieren. Bei der Fabrikatioun vu Réier, duerch de Prozess vun der Isoléierschicht an der Entstoe vun enger grousser Zuel vu positiven Ionen, sou datt op der anerer Säit vun der Interface méi negativ Ladung induzéiert ka ginn, dës negativ Ladungen op déi héich Pénétratioun vu Gëftstoffer am N Regioun verbonne mat der Bildung vun engem konduktiven Kanal, och am VGS = 0 gëtt et och eng grouss Leckstroum ID. wann d'Gate Volt geännert gëtt, gëtt de Montant vun charge entschlof am Kanal och geännert, an der konduktiv Kanal Breet an narrowness vun der Kanal an änneren, an domat der Auswee aktuell ID mat der Gate Volt. aktuell ID variéiert mat der Gatespannung.

Elo d'Applikatioun vunMOSFEThuet d'Leit d'Léieren, d'Aarbechtseffizienz staark verbessert, wärend eis Liewensqualitéit verbessert. Mir hunn e méi rationaliséiert Verständnis dovun duerch e puer einfacht Verständnis. Et gëtt net nëmmen als Instrument benotzt, méi Verständnis vu senge Charakteristiken, de Prinzip vun der Aarbecht, wat eis och vill Spaass gëtt.