D-FET ass an der 0 Gate Bias wann d'Existenz vum Kanal, kann de FET féieren; E-FET ass an der 0 Gate Bias wann et kee Kanal ass, kann de FET net féieren. dës zwou Zorte vu FETs hunn hir eege Charakteristiken a Gebrauch. Am Allgemengen, verstäerkte FET an Héich-Vitesse, niddereg-Muecht Kreesleef ass ganz wäertvoll; an dësem Apparat funktionnéiert, et ass d'Polaritéit vun der Gate Bias voLtage an Drain Spannung vun der selwechter, ass et méi bequem am Circuit Design.

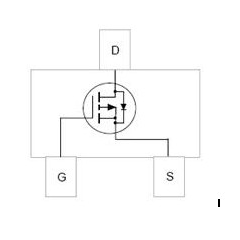

Déi sougenannte verstäerkte Mëttelen: wann VGS = 0 Röhre e ofgeschniddene Staat ass, plus de richtege VGS, ginn d'Majoritéit vun den Träger un d'Paart ugezunn, sou datt d'Träger an der Regioun "verbessert" an e konduktiven Kanal bilden. n-Kanal verstäerkte MOSFET ass am Fong eng lénks-riets symmetresch Topologie, déi de P-Typ Hallefleit bei der Generatioun vun enger Schicht vu SiO2 Filmisolatioun ass. Et generéiert eng isoléierend Schicht vu SiO2 Film um P-Typ Hallefleiter, an diffuséiert dann zwee héich dotéiert N-Typ Regiounen duerchphotolithographie, a féiert Elektroden aus der N-Typ Regioun, eng fir d'Drain D an eng fir d'Quell S. Eng Schicht aus Aluminiummetall gëtt op der Isoléierschicht tëscht der Quell an dem Drain als Paart G. Wann VGS = 0 V plazéiert ass. , ginn et zimmlech vill Dioden mat Réck-zu-Réck-Dioden tëscht dem Drain an der Quell an d'Spannung tëscht D an S mécht kee Stroum tëscht D an S. De Stroum tëscht D an S gëtt net geformt duerch d'Spannung ugewannt.

Wann d'Gatespannung bäigefüügt gëtt, wann 0 <VGS <VGS(th), duerch dat kapazitivt elektrescht Feld, deen tëscht dem Paart an dem Substrat geformt gëtt, ginn d'Polyon Lächer am P-Typ Hallefleit no ënnen vum Paart no ënnen ofgestouss, an eng dënn Ausarmschicht vun negativen Ionen erschéngt; gläichzäiteg, et wäert der oligons dohinner lackele op d'Uewerfläch Layer ze plënneren, mä d'Zuel ass limitéiert an net genuch engem conduktiv Kanal ze Form, datt d'Drain an d'Quell kommunizéieren, sou ass et nach net genuch ze Formatioun vun Drain aktuell ID. weider Erhéijung VGS, wann VGS > VGS (th) (VGS (th) gëtt de Turn-on Volt genannt), well zu dëser Zäit d'Gate Volt relativ staark war, an der P-Typ Hallefleit Uewerfläch Schicht no ënnen vun der Paart ënner der Sammelen vun méi Elektronen, Dir kënnt en Trench bilden, den Drain an d'Quell vun der Kommunikatioun. Wann d'Drain Quell Volt zu dëser Zäit dobäi ass, kann d'Drain Stroum ID geformt ginn. Elektronen am konduktiven Kanal geformt ënner dem Paart, well d'Träger Lach mat der P-Typ Hallefleitpolaritéit Géigendeel ass, sou datt et Anti-Typ Schicht genannt gëtt. Als VGS weider ze Erhéijung, ID wäert weider. ID = 0 bei VGS = 0V, an den Drainstroum geschitt nëmmen nom VGS> VGS (th), also gëtt dës Zort MOSFET Verbesserung MOSFET genannt.

D'Kontrollverhältnis vu VGS um Drainstroum kann duerch d'Kurve beschriwwe ginn iD = f(VGS(th))|VDS=const, wat d'Transferkarakteristikkurve genannt gëtt, an d'Gréisst vum Hang vun der Transfercharakteristikkurve, gm, reflektéiert d'Kontroll vum Drainstroum vun der Gatequellspannung. d'Gréisst vum gm ass mA/V, sou datt gm och d'Transkonduktioun genannt gëtt.